herunterladen

Altera Corporation 1

APEX 20K

Programmable Logic

Device Family

March 2004, ver. 5.1 Data Sheet

DS-APEX20K-5.1

Features

■ Industry’s first programmable logic device (PLD) incorporating

system-on-a-programmable-chip (SOPC) integration

–MultiCore

TM

architecture integrating look-up table (LUT) logic,

product-term logic, and embedded memory

– LUT logic used for register-intensive functions

– Embedded system block (ESB) used to implement memory

functions, including first-in first-out (FIFO) buffers, dual-port

RAM, and content-addressable memory (CAM)

– ESB implementation of product-term logic used for

combinatorial-intensive functions

■ High density

– 30,000 to 1.5 million typical gates (see Tables 1 and 2)

– Up to 51,840 logic elements (LEs)

– Up to 442,368 RAM bits that can be used without reducing

available logic

– Up to 3,456 product-term-based macrocells

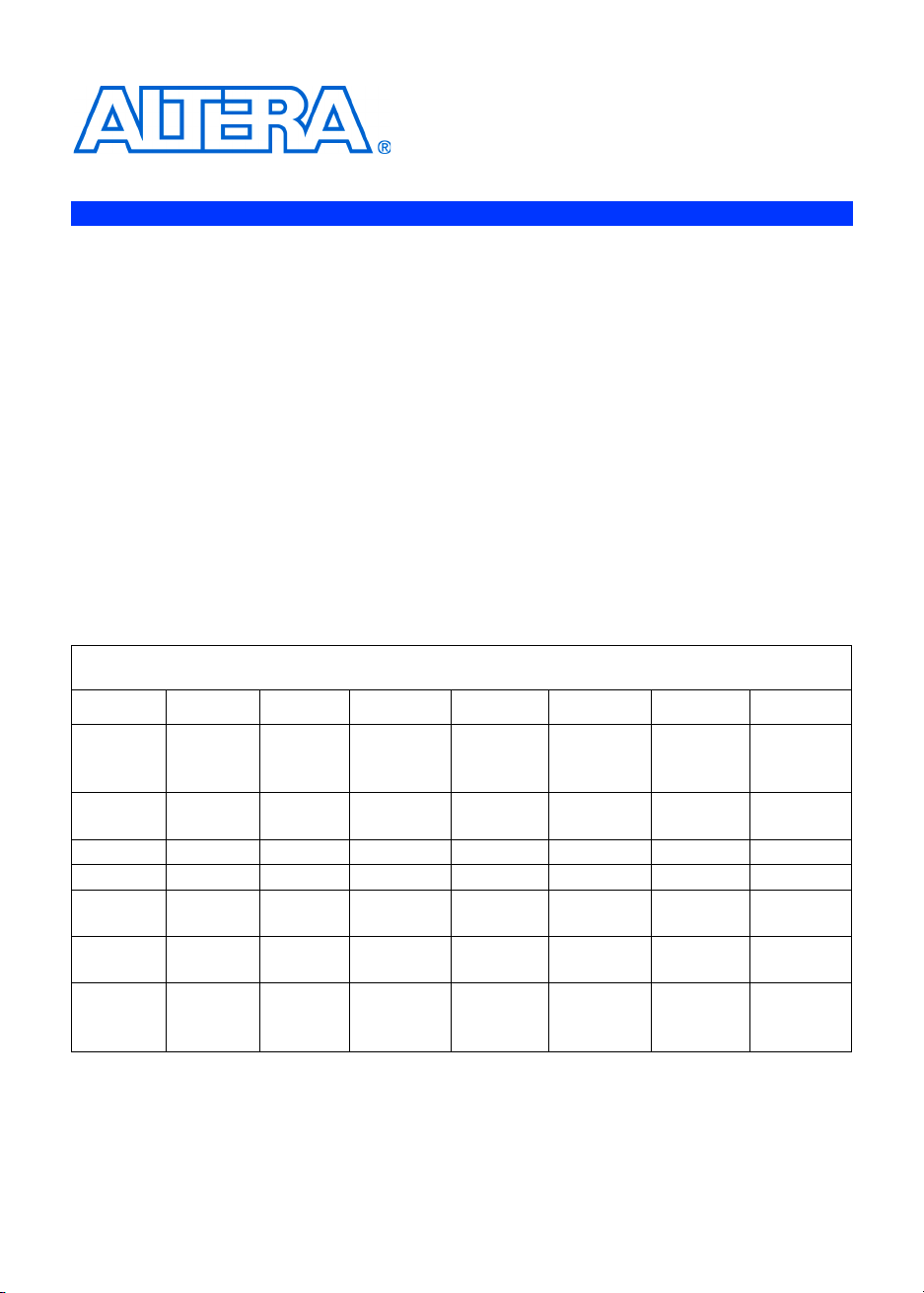

Table 1. APEX 20K Device Features Note (1)

Feature EP20K30E EP20K60E EP20K100 EP20K100E EP20K160E EP20K200 EP20K200E

Maximum

system

gates

113,000 162,000 263,000 263,000 404,000 526,000 526,000

Typical

gates

30,000 60,000 100,000 100,000 160,000 200,000 200,000

LEs 1,200 2,560 4,160 4,160 6,400 8,320 8,320

ESBs 12 16 26 26 40 52 52

Maximum

RAM bits

24,576 32,768 53,248 53,248 81,920 106,496 106,496

Maximum

macrocells

192 256 416 416 640 832 832

Maximum

user I/O

pins

128 196 252 246 316 382 376

Verzeichnis