herunterladen

LTC2656

1

2656fa

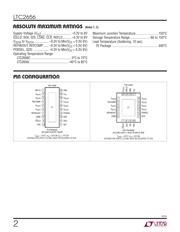

BLOCK DIAGRAM

FEATURES

APPLICATIONS

DESCRIPTION

Octal 16-/12-Bit Rail-to-Rail

DACs with 10ppm/°C

Max Reference

n

Mobile Communications

n

Process Control and Industrial Automation

n

Instrumentation

n

Automatic Test Equipment

n

Automotive

n

Precision 10ppm/°C Max Reference

n

Maximum INL Error: ±4LSB at 16 Bits

n

Guaranteed Monotonic over Temperature

n

Selectable Internal or External Reference

n

2.7V to 5.5V Supply Range (LTC2656-L)

n

Integrated Reference Buffers

n

UltralowCrosstalkBetweenDACs(<1nV•s)

n

Power-On-Reset to Zero-Scale/Mid-scale

n

Asynchronous LDAC Update Pin

n

Tiny 20-Lead 4mm × 5mm QFN and 20-Lead

Thermally Enhanced TSSOP Packages

The LTC

®

2656 is a family of octal 16-/12-bit rail-to-rail

DACs with a precision integrated reference. The DACs have

built-in high performance, rail-to-rail, output buffers and

are guaranteed monotonic. The LTC2656-L has a full-scale

output of 2.5V with the integrated 10ppm/°C reference and

operates from a single 2.7V to 5.5V supply. The LTC2656-H

has a full-scale output of 4.096V with the integrated refer-

ence and operates from a 4.5V to 5.5V supply. Each DAC can

also operate with an external reference, which sets the DAC

full-scale output to two times the external reference voltage.

These DACs communicate via a SPI/MICROWIRE

™

com-

patible 4-wire serial interface which operates at clock rates

up to 50MHz. The LTC2656 incorporates a power-on reset

circuit that is controlled by the PORSEL pin. If PORSEL

is tied to GND the DACs reset to zero-scale. If PORSEL is

tied to V

CC

, the DACs reset to mid-scale.

REGISTER

REGISTER

INTERNAL REFERENCE

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

DECODECONTROL LOGIC

POWER-ON RESET

32-BIT SHIFT REGISTER

REFCOMP REFIN/OUT

V

CC

GND

DAC A

REF

REF

REF

REF

REF

REF

REF

REF

DAC H V

OUTH

DAC G V

OUTG

DAC F V

OUTF

DAC E V

OUTE

PORSEL

SDO

SDI

2656 TA01a

CLR

REFLO

V

OUTA

DAC B

V

OUTB

DAC C

V

OUTC

DAC D

V

OUTD

SCK

LDAC

CS/LD

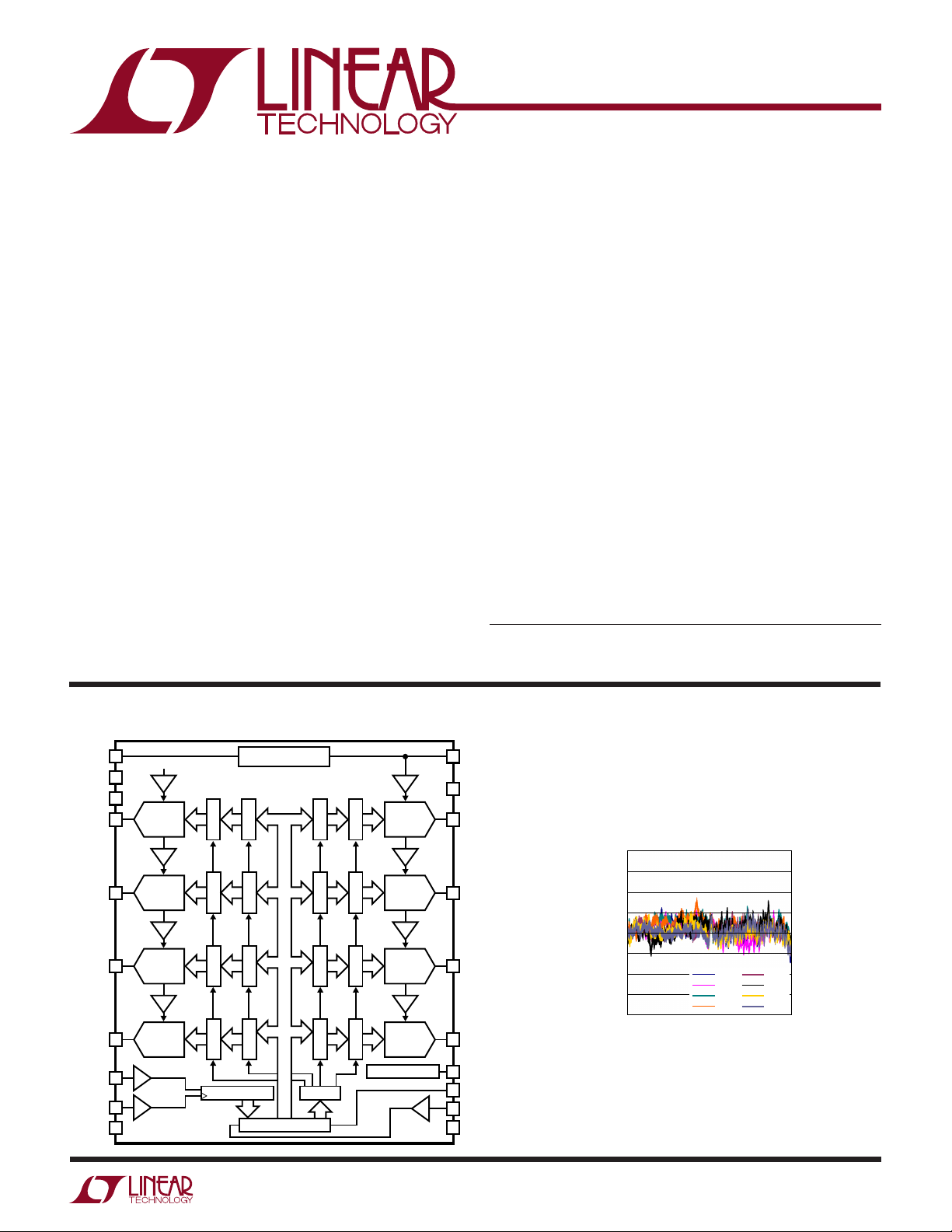

CODE

128

INL (LSB)

0

1

2

65535

2656 TA01b

–1

–2

–4

16384

32768

49152

–3

4

3

DAC A

DAC B

DAC C

DAC D

DAC E

DAC F

DAC G

DAC H

INL vs Code

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear

Technology Corporation. All other trademarks are the property of their respective owners.

Protected by U.S. Patents, including 5396245, 6891433.

Verzeichnis

- ・ Konfiguration des Pinbelegungsdiagramms on Seite 15

- ・ Abmessungen des Paketumrisses on Seite 24

- ・ Paket-Footprint-Pad-Layout on Seite 23

- ・ Teilenummerierungssystem on Seite 4

- ・ Markierungsinformationen on Seite 4

- ・ Blockdiagramm on Seite 1 Seite 16 Seite 19

- ・ Typisches Anwendungsschaltbild on Seite 26

- ・ Technische Daten on Seite 9 Seite 18

- ・ Anwendungsbereich on Seite 1

- ・ Elektrische Spezifikation on Seite 5 Seite 6 Seite 7 Seite 8 Seite 9