herunterladen

1. General description

The LPC1769/68/67/66/65/64/63 are ARM Cortex-M3 based microcontrollers for

embedded applications featuring a high level of integration and low power consumption.

The Arm Cortex-M3 is a next generation core that offers system enhancements such as

enhanced debug features and a higher level of support block integration.

The LPC1768/67/66/65/64/63 operate at CPU frequencies of up to 100 MHz. The

LPC1769 operates at CPU frequencies of up to 120 MHz. The Arm Cortex-M3 CPU

incorporates a 3-stage pipeline and uses a Harvard architecture with separate local

instruction and data buses as well as a third bus for peripherals. The Arm Cortex-M3 CPU

also includes an internal prefetch unit that supports speculative branching.

The peripheral complement of the LPC1769/68/67/66/65/64/63 includes up to 512 kB of

flash memory, up to 64 kB of data memory, Ethernet MAC, USB Device/Host/OTG

interface, 8-channel general purpose DMA controller, 4 UARTs, 2 CAN channels, 2 SSP

controllers, SPI interface, 3 I

2

C-bus interfaces, 2-input plus 2-output I

2

S-bus interface,

8-channel 12-bit ADC, 10-bit DAC, motor control PWM, Quadrature Encoder interface,

four general purpose timers, 6-output general purpose PWM, ultra-low power Real-Time

Clock (RTC) with separate battery supply, and up to 70 general purpose I/O pins.

The LPC1769/68/67/66/65/64/63 are pin-compatible to the 100-pin LPC236x Arm7-based

microcontroller series.

For additional documentation, see Section 19 “

References”.

2. Features and benefits

Arm Cortex-M3 processor, running at frequencies of up to 100 MHz

(LPC1768/67/66/65/64/63) or of up to 120 MHz (LPC1769). A Memory Protection Unit

(MPU) supporting eight regions is included.

Arm Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator

enables high-speed 120 MHz operation with zero wait states.

In-System Programming (ISP) and In-Application Programming (IAP) via on-chip

bootloader software.

On-chip SRAM includes:

32/16 kB of SRAM on the CPU with local code/data bus for high-performance CPU

access.

LPC1769/68/67/66/65/64/63

32-bit Arm Cortex

®

-M3 microcontroller; up to 512 kB flash and

64 kB SRAM with Ethernet, USB 2.0 Host/Device/OTG, CAN

Rev. 9.8 — 4 May 2018 Product data sheet

Verzeichnis

- ・ Konfiguration des Pinbelegungsdiagramms on Seite 7 Seite 8 Seite 10 Seite 11 Seite 12

- ・ Abmessungen des Paketumrisses on Seite 78 Seite 79 Seite 80

- ・ Teilenummerierungssystem on Seite 4

- ・ Markierungsinformationen on Seite 5

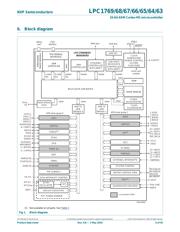

- ・ Blockdiagramm on Seite 6

- ・ Schweißen Temperatur on Seite 81 Seite 82 Seite 83 Seite 84 Seite 85

- ・ Beschreibung der Funktionen on Seite 1 Seite 21

- ・ Technische Daten on Seite 90

- ・ Anwendungsbereich on Seite 4 Seite 90