herunterladen

Philips Semiconductors Application note

AN240Interfacing 3V and 5V applications

Authors: Tinus van de Wouw (Nijmegen) / Todd Andersen (Albuquerque)

11-1

1995 Sep 15

1.0 THE NEED FOR INTERFACING BETWEEN 3V

AND 5V SYSTEMS

Many reasons exist to introduce 3V

1

systems, notably the lower

power consumption for mobile applications and the introduction of

parts that use technologies with such fine geometries that 5V is

simply not allowed any more.

The introduction of the 3V standard as supply voltage has resulted

in many design activities for digital systems. Very often, however,

there is a gradual transition from 5V to 3V, since not always are all

required components available, or the system is rather complex so

that 3V is introduced in part of a system. As an example, customers

wish to use an existing and proven CPU, while a new, more complex

ASIC with added features can only be made with 3V. Or vice versa!

With the introduction of new standards such as 2.2-2.7V or even

1.7V we expect that interfacing between systems that use different

supply voltages will be an actual issue for many years to come. This

application note specifically addresses the interfacing between 3V

and 5V systems, but the results can be applied for interfacing

between other voltage levels as well.

We will discuss how one can ensure reliable information exchange

and how to prevent current flow between both supply voltages when

interfacing logic with memories, ASICs, PLDs and microprocessors

at different supply voltages.

2.0 LEVEL SHIFTING - INPUT AND OUTPUT

LEVELS

We obviously want a reliable signal transfer from the 5V system to

the 3V system and vice versa. This implies that the output voltages

should be such that the input levels are exceeded.

2.1 TTL and CMOS Switching Levels

As a reminder, digital circuits have input levels defined: one voltage

(V

IL

) below which the circuit certainly sees it as a logical “0” and

another voltage (V

IH

) above which the input is guaranteed “1”.

Digital circuits normally come in two versions:

•TTL levels: V

IL

= 0.8V, V

IH

= 2.0V

•CMOS levels: V

IL

= 0.3 V

CC

, V

IH

= 0.7 V

CC

.

For systems with V

CC

= 5.0 0.5V this practically means:

V

IL

= 1.35V, V

IH

= 3.85V.

2.2 Level Shifting from 5V to 3V

All 5V families have an output voltage swing that is large enough to

drive 3V reliably. As described in Section 4.0, outputs may be as

high as 3.5V for many “TTL” output stages, to the full 5V for many

CMOS outputs. Therefore, as far as switching levels are concerned,

there are no problems in interfacing from 5V to a 3V system.

2.3 Level Shifting from 3V to 5V

All 3V logic families deliver practically the full output voltage swing of

3V, so they can drive TTL switching levels without problems (see

Fig. 1).

2V

0.8V

SV00084

70%

30%

V

CC

GND

3.3V

OUTPUT

CMOS

LEVELS

TTL

LEVELS

Figure 1. Switching Levels

One issue remains: a 3V system driving a 5V one that has CMOS

input levels. This cannot be reliably done by standard 3V logic

families, even when using pull-up resistors, simply because under

worst case conditions, the output voltage is not high enough to

guarantee that the signal will be seen as a logical “1”. Philips

Semiconductors developed special dual V

CC

levelshifters to address

that situation (see Section 6.0).

3.0 INPUT STRUCTURES OF DIGITAL CIRCUITS

Before discussing further issues on 3-5V interfacing we should start

by investigating the inputs of digital circuits in order to understand

what care one should take to prevent problems.

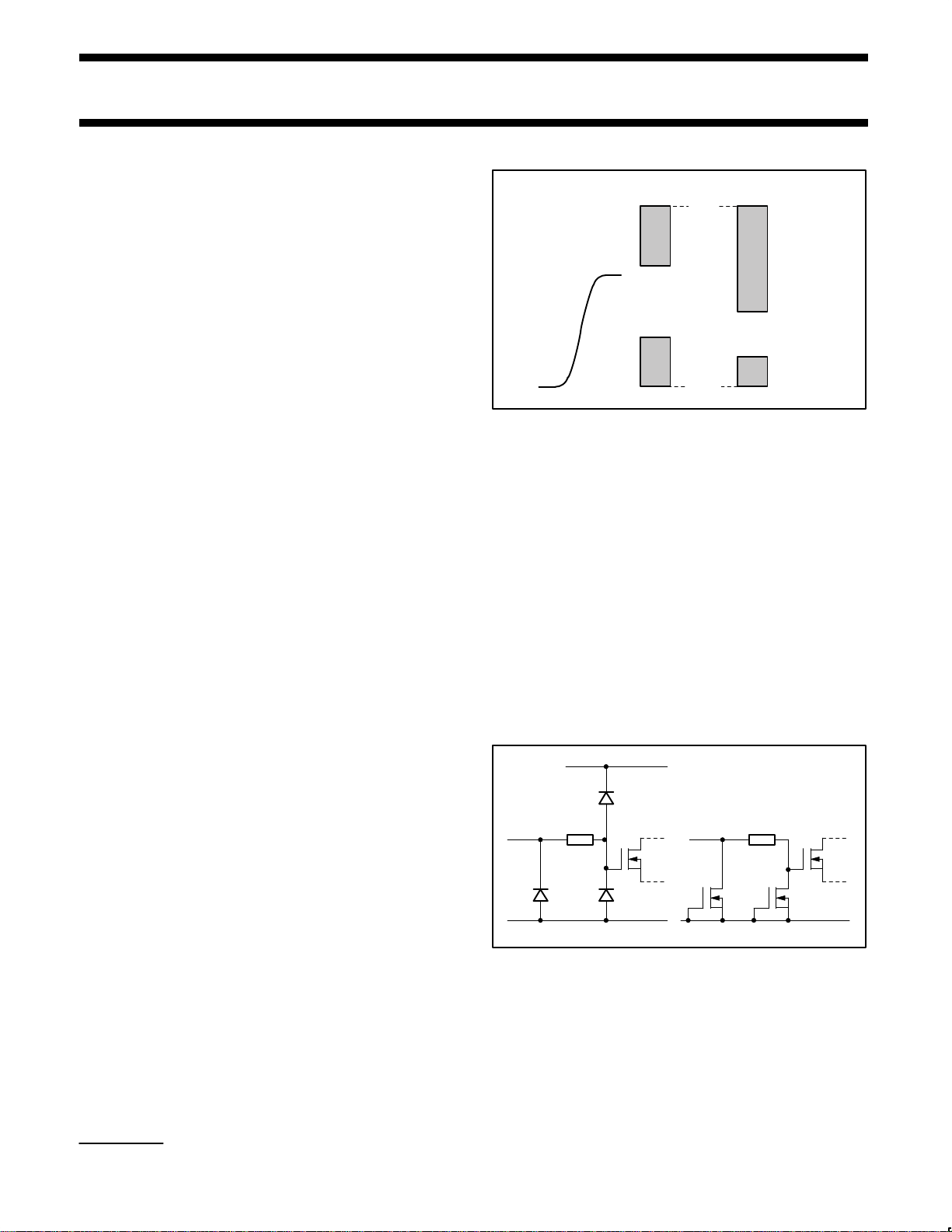

3.1 ESD Input Protection Circuits

Virtually all inputs of a digital circuit contain an ESD protection circuit

that prevents damage against electrostatic discharge. This circuit is

present between the physical input pin and the active circuit. Two

popular schemes are given in Fig. 2.

V

CC

R

S

INPUT

R

S

INPUT

SV00081

Figure 2. ESD Protection Circuits

The classic CMOS scheme as shown left provides protection

against negative zaps by the diodes to ground. Positive zaps are

clamped by the diode to V

CC

. The real disadvantage is that the

maximum input voltage of such a circuit is limited to V

CC

+ 0.5V. For

a V

CC

of 3V the allowed input voltage is too low for direct interfacing

to most 5V systems.

1. We use the expression “3V” when a supply voltage is used between 2.7 and 3.6V.